シャープ技報 第91号・2005年4月

# 1ビットオーディオアンプ用ΔΣ変調器

A Delta-Sigma Modulator for 1-Bit Audio Amplifier

ロレ パスカル\* Lo Ré Pascal 藤 本 義 久\*

宮本雅之\*

Yoshihisa Fujimoto Masayuki Miyamoto

# 要旨

1 ビットオーディオアンプ用 7 次  $\Delta$  Σ 変調器を開発した。システム設計において 7 次  $\Delta$  Σ 変調器の回路パラメータを最適化することにより、SNR 1 1 1 dB、発振限界 0.89、THD+N(歪特性)0.0015%を実現した。また、 $\Delta$  Σ 変調器に用いられるコンパレータ部にフィードバック部を設けることにより、回路バラツキの影響を低減することができた。0.35  $\mu$  mCMOS プロセスで試作したチップの面積は 12.6 mm² である。消費電流は 60 mA、電源電圧は 5 V である。

A  $7^{\text{th}}$  order single-loop single-bit Delta-Sigma Modulator (DSM) for 1-Bit Digital Audio Switching Amplifier (DSA) is presented. To achieve high SNR and ensure the modulator stability for a large input range, the positions of the modulator loop filter poles and zeros are optimized, and a feedback comparator is used. A test chip was fabricated in a 0.35- $\mu$ m CMOS process with optional 5-V transistors. The modulator achieves a SNR of 111 dB and 0.0015% THD+N over the audio band. The normalized maximum allowable input range is 0.89. The chip area is 12.6 mm² and it draws 60 mA from a 5-V supply.

#### まえがき

音声再生装置には、スピーカを駆動し電力増幅を 行うパワーアンプという回路が必要となる。従来よ りパワーアンプとしてリニアアンプが幅広く利用さ れているが,電力効率が低く,低消費電力化を実現す るのが困難である。また、放熱のためのコスト増大を 招く。効率およびコストの問題を解決する手法の1 つとして1ビットスイッチングアンプが開発された。 1ビットスイッチングアンプは、入力された音声信 号を1ビットデジタル信号に変換するための変調器 とスピーカを駆動するためのパワースイッチから構 成される。スピーカに伝達される信号はデジタル信 号であるため、パワースイッチによる電力ロスはリ ニアアンプに比べて小さく, 高電力効率を実現する ことができる。理論的には、B級リニアアンプの最大 電力効率が78.6%1)であるが、1ビットスイッチン グアンプでは最大電力効率が100%となる。

入力信号を 1 ビットデジタル信号に変換するための方式として、パルス幅変調(PWM: Pulse Width Modulation) 及びパルス密度変調 (PDM: Pulse Density

今回,我々は高電力効率,低コスト,高性能を実現する1 ビットスイッチングアンプ用 $\Delta$   $\Sigma$ 変調器の開発を行った。 $\Delta$   $\Sigma$ 変調器のフィードバックループにパワースイッチを配置することで111dBの SNR を達成した。さらに, $\Delta$   $\Sigma$ 変調器を用いる場合に生じる不安定性の問題を回避するため, $\Delta$   $\Sigma$ 変調器に用いられるループフィルタの設計方法およびコンパレータの構成を工夫し,高電力効率化を実現することが可能であることを確認した。

以下に、開発した1ビットスイッチングアンプ用 $\Delta$  $\Sigma$ 変調器の概要、及び高性能・高電力効率化技術について述べる。

<sup>\*</sup> 技術本部 デバイス技術研究所 第4研究室

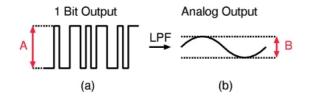

図1 1 ビット信号とアナログ出力 Fig. 1 1-Bit signal and analog output.

# 1. 1ビットスイッチングアンプ

ΔΣ変調器を用いる1ビットスイッチングアンプ は、高効率、低コスト、高性能を実現することが可能 である。しかし、ΔΣ変調器を用いた1ビットスイッ チングアンプ (以下、1ビットアンプと記載する) に は2つの問題点がある。1つは、パワースイッチのス イッチング動作により発生するノイズによる SNR の 劣化である。パワースイッチのスイッチング動作によ り発生するノイズは、スピーカに伝達されるため高い SNRを実現できない。もう1つは、レベルの高い音声 信号が入力される場合にΔΣ変調器が発振するという 不安定性の問題である。△∑変調器が発振する場合に はノイズシェーピング特性が得られず、極端に SNR が劣化する。高電力効率を達成するためには、レベル の高い音声信号が入力される場合においても△∑変調 器が発振しないことが必要である。1 ビットアンプに 正弦波が入力される場合の,1ビットアンプの出力信 号の代表的な波形を図1に示す。

図1 (a) はパワースイッチから出力される1ビットデジタル信号の波形を示しており、図1 (b) はその1ビットデジタル信号を高域の成分を除去するローパスフィルタに通した後の信号の波形を示す。また、図1 (a) における1ビットデジタル信号の振幅および図1 (b) における正弦波の振幅をそれぞれAおよびBとする。ここで、発振限界TEを次式で定義する。

### TE = B/A

理想的には発振限界=1を実現することが可能であるが、上述したように $\Delta$ Σ変調器には不安定性の問題があるため、発振限界<1となり、1ビットアンプの電力効率が落ちる。

以下に,高 SNR (111dB),発振限界 (0.89) を実現 する 1 ビットオーディオアンプ用  $\Delta$   $\Sigma$  変調器について 述べる。

# 2. ΔΣ変調器の目標仕様

1ビットアンプ用 $\Delta$   $\Sigma$ 変調器を下記項目・仕様に基づいて設計する。

- ・信号帯域は音声帯域の全体, つまり 10Hz から 22kHz までとする。

- ・一般に使われる音源の SNR が 100dB 程であることから, 設計マージンを加えて,  $\Delta \Sigma$  変調器の SNR を 112dB とする。

- ・帯域内の出力ノイズがフラットになり、かつ、トーンが発生しないように  $\Delta \Sigma$  変調器を設計をする。

- ・ワンチップに右と左チャネル用の $\Delta \Sigma$ が含まれるため,左右のチャネル間のリークが起こらないようにチップのレイアウトを考慮する。

# 3. 1ビットオーディオアンプのアーキテクチュア

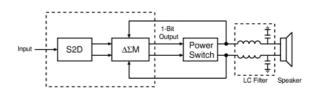

図2に我々が開発した $\Delta$  Σ変調器と周辺回路から構成される1 ビットオーディオアンプのブロック図を示す。電源変動等に起因する外来ノイズの影響を減らすため、 $\Delta$  Σ変調器はフル差動回路で構成するが、システムの入力がシングルエンド信号となるため、 $\Delta$  Σ変調器の前段にシングル差動変換器(S2D: Single-To-Differential)を設ける。また、今回の設計ではS2Dのゲインを12dBに設定する。 $\Delta$  Σ変調器はS2Dにより生成された差動信号を、フルブリッジ構成のパワースイッチ段を駆動する1 ビットデジタル信号に変換する。パワースイッチの出力がインダクタとキャパシタから構成されるローパスフィルタを通してスピーカへ伝達される。今回試作したチップには $\Delta$  Σ変調器と共にS2D も搭載されている。

パワースイッチより混入するスイッチングノイズを 低減するため、 $\Delta \Sigma$ 変調器のノイズシェーピング特性 を利用する。

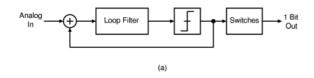

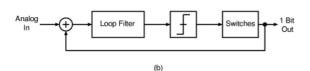

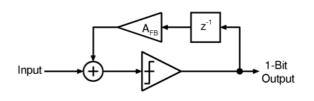

図3 (a) に一般的な1ビットスイッチングアンプのブロック図を示す。入力信号がループフィルタ及び量子化器から構成されるΔΣ変調器によりパワースイッチを駆動する1ビットデジタル信号に変換される。量子化器の出力をループフィルタの入力部へ帰還

図2 1 ビットオーディオアンプのアーキテクチュア Fig. 2 Overall architecture of the DSM based 1-Bit DSA.

シャープ技報 第91号・2005年4月

図3 従来の1ビットスイッチングアンプモデル(a)と開発 した1ビットスイッチングアンプモデル(b)

Fig. 3 Standard DSM based amplifier model (a) and modified amplifier model (b).

することより、音声帯域の量子化ノイズを低減することができる。しかし、図3(a)の構成では、パワースイッチにより混入するスイッチングノイズが出力信号に混入してしまう。このノイズを音声帯域において低減させるため、図3(b)に示すようにパワースイッチを $\Delta\Sigma$ 変調器のループ内に含める。図3(b)の構成では、量子化ノイズと共にパワースイッチにより混入するスイッチングノイズもシェーピングされるため、音声帯域において出力端子に現われるスイッチングノイズを低減することができる。

# 4. ΔΣ変調器

アナログデジタル変換器として使われる $\Delta$   $\Sigma$ 変調器を設計するとき、量子化器のビット数、オーバーサンプリング比(OSR: Over-Sampling Ratio)、ループフィルタの次数など、様々なパラメータを決定する必要がある。1 ビットアンプ用 $\Delta$   $\Sigma$ 変調器では、量子化器のビット数は1 ビットである必要がある。また、OSRが高い場合パワースイッチの動作周波数が高くなりパワースイッチの入力容量による電力ロスが大きくなるため、OSRをできるだけ小さくすることが好ましい。

設計した  $\Delta$   $\Sigma$  変調器では OSR を 128 とし,  $\Delta$   $\Sigma$  変調器 のサンプリング周波数は 5.6 MHz とする。次に,目標の SNR 及び発振限界を達成するためループフィルタの次数を決める必要がある。 OSR=128 と 3 次のループフィルタを用いた  $\Delta$   $\Sigma$  変調器により 110 dB 以上の SNR を実現することは可能である  $^3$  。しかし,SNR と発振限界にトレードオフがある。例えば,OSR=40,6次の  $\Delta$   $\Sigma$  変調器では SNR が 105 dB になるが,発振限界が 0.5 となってしまう  $^3$  。高い SNR および高い発振限界を実現するため,我々は 7 次のループフィルタを使用することにした。

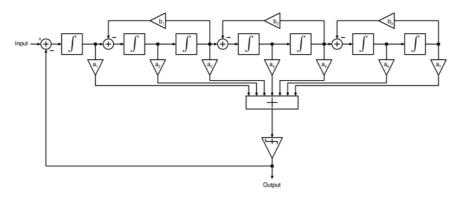

図4に $\Delta$  Σ変調器の詳細なブロック図を示す。本 $\Delta$  Σ変調器は3つのローカルフィードバックを有する7次のフィードフォワード型ループフィルタと1ビットコンパレータから構成される。

# 4・1 ノイズ伝達関数 (NTF:Noise Transfer Function) の設計

Matlab ツール (Mathworks 社製) を用いて, NTFの極と零点の設計を行った。

上述のように、オーディオ帯域内のノイズフロアをできるだけフラットにする必要がある。 $\Delta \Sigma$ 変調器の零点を全てDCに配置する場合には、ノイズフロアが帯域内において上昇する。従って、零点を音声帯域内に分散させる必要がある。**図 4** に示すローカルフィードバックを用いることにより、NTFの零点をDC以外に配置することが可能となり、音声帯域内のノイズフロアをフラットにすると共に SNR を改善することができる。ノイズシェーピングによる量子化ノイズの盛り上がりが帯域外の周波数から現われるように、1つの零点の周波数が 22kHz より高い周波数になるように設計する。配置した 3 つの零点の周波数はそれぞれ 10.39kHz, 17.00kHz 及び 24.76kHz である。

次に下記2つ条件に基づいてシミュレーションにより最適な極の値を決定する。その1つ目は、目標の発振限界を確保するため、高いレベルの信号を入力して

図4 ΔΣ変調器のブロック図

Fig. 4 Block diagram of the Delta Sigma Modulator.

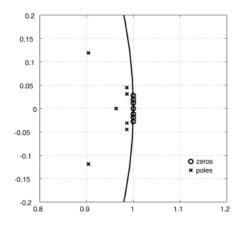

図5 Z領域における極および零点の配置 Fig. 5 z-domain pole/zero plot.

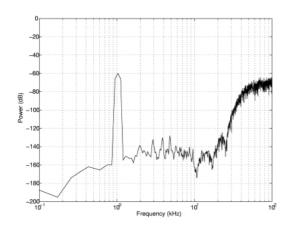

図 6 出力スペクトルのシミュレーション結果 Fig. 6 Simulated output spectrum for a -60-dBFS input.

も  $\Delta \Sigma$ 変調器が不安定にならないことである。2つ目は,  $\Delta \Sigma$ 変調器がパワースイッチによる遅延の影響を受けないことである。 $\mathbf{Z}$  5 に  $\mathbf{Z}$  領域における設計した NTF の極および零点の配置を示す。

図6に-60dBFS, 1kHzの正弦波を入力したときの出力スペクトルのシミュレーション結果を示す。帯域内においてフラットな量子化ノイズの分布を実現できていることが分かる。また、このときのSNRは122dBである。また、発振限界のシミュレーション結果は0.92である。

#### 4・2 コンパレータ

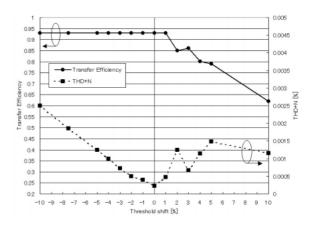

発振限界を改善するため、コンパレータの閾値を制御する方法を提案する。一般にコンパレータはその閾値が前の出力値に依存して変化する特性(閾値シフト)を有する。閾値シフトがΔΣ変調器の発振限界及び歪に与える影響をシミュレーションにより確認した。図7に、発振限界及び歪特性(THD+N:Total Harmonic Distortion and Noise)と閾値シフトの関係を示す。図7のグラフにおいて、横軸に示した閾値シフ

図 7 発振限界及び THD+N と閾値シフトの関係 Fig. 7 Transfer efficiency as a function of the comparator threshold shift.

トが1%となる場合は、コンパレータの閾値が出力電 圧のフルスケールの1%変化することを意味する。一 般に、コンパレータの閾値シフトは正または負になる 可能性がある。図7に示すように、閾値シフトが1% を超えるところから発振限界が急激に劣化する。逆 に、閾値シフトが負の場合、発振限界が殆ど変化せず 一定となる。閾値シフトが負となる領域を使えばプロ セスバラツキにより閾値シフトが変化しても発振限界 は一定となる。ただし、閾値シフトが小さくなりすぎ ると, 歪が発生して, THD+Nが劣化する。コンパレー タの出力信号を入力信号にフィードバックすることよ り、閾値シフトを所望の値に設定することができる。 閾値シフトを-1%(設計値)とすると、発振限界は 0.92となる。また、このときの歪の劣化はほとんどな い。図8にフィードバックコンパレータのブロック図 を示す。一般のコンパレータの出力を遅延段及びゲイ ン段を通して帰還する。ゲインA<sub>FR</sub>の値に応じて閾値 のシフトを制御できる。

## 4・3 回路設計

スイッチトキャパシタ回路技術を用いて 0.35-  $\mu$  m CMOSプロセスで  $\Delta$   $\Sigma$ 変調器を試作した。  $\Delta$   $\Sigma$ 変調器 のゲイン係数を Polysilicon-Insulator-Polysilicon (PIP) キャパシタの比で実現した。 回路ノイズ,素子のミス

図8 フィードバックコンパレータのブロック図 Fig. 8 Block diagram of the feedback comparator.

シャープ技報 第91号・2005年4月

図9 最終段の加算器およびフィードバックコンパレータの回 路図

Fig. 9 Simplified schematic of the adder-comparator.

マッチなどにより性能が劣化するため,量子化ノイズによる SNR を目標より 10dB 高い 122dB に設定してゲイン係数を決定した。設計時間を短縮するため Verilog-Aモデルを用いてSpiceシミュレーションを行い, $\Delta \Sigma$ 変調器のトータル性能を確認した。

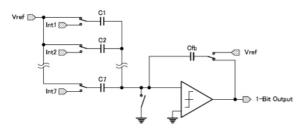

図9に最終段の加算器およびフィードバックコンパレータの回路図を示す。図9に示した回路はシングルエンド回路として示しているが、実際の回路はフル差動回路にしている。積分器の出力をスイッチトキャパシタC1~C7により重み付け加算する。

コンパレータは入力増幅器と一般のトラックアンド

ラッチ段から構成される。閾値シフトを制御するゲイン  $A_{FB}$  はスイッチトキャパシタ Cfb により実現される。

# 5. 測定結果

$\Delta$   $\Sigma$ 変調器の性能評価において、評価ボードに搭載されている水晶発振素子と試作 IC に搭載されるインバータから構成される水晶発振器により生成された 5.6MHz 信号を  $\Delta$   $\Sigma$ 変調器のクロックとして使う。フルスケール入力を  $\Delta$   $\Sigma$ 変調器の安定動作を確保する最大入力と定義する。オーディオアナライザを用いて AES17 規格 $^4$ )に基づく測定を行った。AES17 規格によると、SNR の測定時は  $^6$ 0dBV、997Hz の正弦波を入力する。また、THD+N の測定時はフルスケール、997Hzの正弦波を入力する。この測定はウェートフィルタなしで行った。上記SNR 及びTHD+Nの測定を以下の  $^6$ 2つ方法を用いて測定した。

・オーディオアナライザに内臓されている二乗平均 メータ (RMS: Root Mean Square)を用いた方式。20kHz から急峻なフィルタを用いてシェーピングによる帯域 外ノイズを削除し、出力信号に含まれるノイズパワー

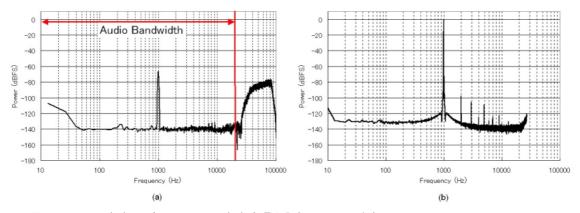

図 10 -60dBV (a) 及びフルスケール (b) 信号を入力したときの出力スペクトル

Fig. 10 Output spectrum for a -60-dBV input tone at 997 Hz (a) and a full-scale input tone at 997 Hz (b).

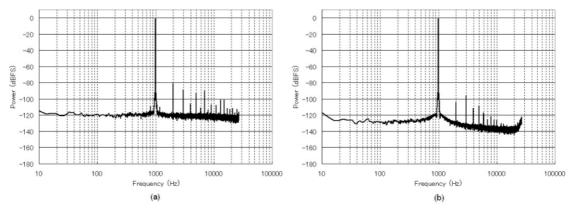

図 11  $\Delta \Sigma$ 変調器の出力信号(a) またはインバータの出力信号(b) をフィードバックする構成の歪特性

Fig. 11 Distortion measurement with the feedback applied after the DSM (a) and after the power switch stage (b).

を測定する。このとき、出力信号に含まれる周波数が997Hzである信号をノッチフィルタで除去する。

・フーリエ変換(FFT: Fast Fourier Transform)によるスペクトル解析を用いた方式。オーディオアナライザで計算したスペクトルを Excel で処理する。ノイズを計算するとき入力信号をスペクトルから削除する。オーディオアナライザの制御とExcelによるデータ処理を Visual Basic スクリプトで記述し自動測定を行った。

図10 (a) 及び図10 (b) に、-60dBVとフルスケール信号を入力した場合の $\Delta$  Σ変調器単体の出力スペクトルをそれぞれ示す。 SNR は 111dB、THD+N は 0.0015%となる。図10 (a) に示したスペクトル図より 25kHz の周波数付近からノイズの盛り上がりを確認できる(ノイズシェーピング特性)。また、音声帯域内のノイズフロアはフラットであり、トーンが存在しないことが確認できる。図10 (a) と図6のスペクトル図を比較することにより、設計通りのノイズシェーピング特性が得られたことが分かる。

パワースイッチより混入するスイッチングノイズを減らすため図 2 に示す構成を採用する。スイッチングノイズ低減効果を確認するため,以下の 2 つの構成で THD+N を測定した。この測定では,パワースイッチとしてインバータ I C (TC74VHC04F)を用いた。図 3 (a) に示すように  $\Delta$   $\Sigma$  変調器の出力信号を  $\Delta$   $\Sigma$  変調器の入力部にフィードバックして,インバータの出力信号を測定した場合のスペクトルを図 11 (a) に示す。THD+N = 0.0147% が得られた。続いて,図 3 (b) に示すようにインバータの出力信号をフィードバックする構成の場合のスペクトルを図 11 (b) に示す。THD+N = 0.0027% が得られた。図 2 の構成を用いることによりスイッチングノイズを約 1/5.5 に低減することができる。

発振限界を測定するため、フルスケール信号を $\Delta\Sigma$ 変調器に入力し、 $\Delta\Sigma$ 変調器の1ビット出力信号を2次RCローパスフィルタに通した後の信号の最大振幅値と $\Delta\Sigma$ 変調器の1ビット出力信号の振幅をそれぞれ測定し、その比である発振限界値を求めた。その結果、発振限界=0.89となった。右と左チャンネルのアイソレーションを測定するため、右チャネルにフルスケール、997Hzの正弦波を入力し、左チャネルの入力レベルをゼロに設定し、左チャネルの $\Delta\Sigma$ 変調器の出力に現れる出力信号レベルを測定した。その結果、アイソレーションが 135dB 以上であることが確認できた。

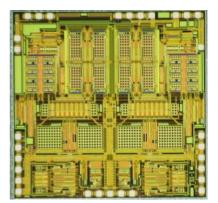

電源電圧5Vにおける右及び左チャンネルの $\Delta \Sigma$ 変調器の消費電流は60mAであり、チップ面積は $12.6mm^2$ である。**写真 1**に試作チップを示す。目標仕

表 1 ΔΣ仕様,シミュレーション値と測定結果

Table 1 Target, Simulation and Measurement results.

| Value               | Target | Matlab Simulation | Measurement          |

|---------------------|--------|-------------------|----------------------|

| SNR                 | 112 dB | 122 dB            | 111 dB               |

| THD+N               | _      | 0.0006 %          | 0.0015 %             |

| Transfer Efficiency | 0.9    | 0.92              | 0.89                 |

| L-R Isolation       | _      | _                 | > 135 dB             |

| Current Consumption | _      | 57 mA (Spice)     | 60 mA                |

| Die Area            | _      | _                 | 12.6 mm <sup>2</sup> |

写真 1 試作チップ Photo 1 Chip micrograph.

様及び測定結果を表1にまとめる。

# むすび

1 ビットオーディオアンプ用の 7 次  $\Delta$  Σ 変調器を試作した。高い発振限界と高い SNR を実現するため,ループフィルタの極の最適化とフィードバックコンパレータを採用した。SNRは111dB, THD+Nは0.0015%,発振限界は0.89である。0.35  $\mu$  mCMOS プロセスを用いて試作したチップの面積は12.6mm²である。消費電流は60mA,電源電圧が5Vである。

# 参考文献

- P. Gray and R. Meyer, "Analysis and Design of Analog Integrated Circuits", John Wiley & Sons (1993).

- H. Ballan and M. Declercq, "12V Σ-Δ class-D amplifier in 5V CMOS technology", IEEE CICC 1995 Proceedings, paper 26.5 (1995).

- S. Norsworthy, R Schreier and G.C. Temes, "Delta-Sigma Data Converters: Theory, Design, and Simulation", IEEE Press (1997).

- 4) AES17-1998, "AES standard method for digital audio engineering Measurement of digital audio equipment", (online) available from <a href="http://www.aes.org/standards/b\_pub/aes17-1998-r2004.pdf">http://www.aes.org/standards/b\_pub/aes17-1998-r2004.pdf</a>> (2004).

(2005年1月26日受理)